# **Tensor Comprehensions: Framework-Agnostic High-Performance Machine Learning Abstractions**

#### Nicolas Vasilache

Facebook AI Research ntv@fb.com

# Oleksandr Zinenko

Inria & ENS, DI oleksandr.zinenko@inria.fr

#### **Theodoros Theodoridis**

ETH Zürich theodort@student.ethz.ch

# Priva Goval

Facebook AI Research prigoyal@fb.com

### **Zachary DeVito**

Facebook AI Research zdevito@fb.com

### William S. Moses

MIT CSAIL wmoses@mit.edu

### Sven Verdoolaege

Polly Labs & Facebook AI Research sven.verdoolaege@gmail.com

### **Andrew Adams**

Albert Cohen Facebook AI Research Inria & ENS, DI & Facebook AI Research andrew.b.adams@gmail.com albert.cohen@inria.fr

### Abstract

Deep learning models with convolutional and recurrent networks are now ubiquitous and analyze massive amounts of audio, image, video, text and graph data, with applications in automatic translation, speech-to-text, scene understanding, ranking user preferences, ad placement, etc. Competing frameworks for building these networks such as TensorFlow, Chainer, CNTK, Torch/PyTorch, Caffe1/2, MXNet and Theano, explore different tradeoffs between usability and expressiveness, research or production orientation and supported hardware. They operate on a DAG of computational operators, wrapping high-performance libraries such as CUDNN (for NVIDIA GPUs) or NNPACK (for various CPUs), and automate memory allocation, synchronization, distribution. Custom operators are needed where the computation does not fit existing high-performance library calls, usually at a high engineering cost. This is frequently required when new operators are invented by researchers: such operators suffer a severe performance penalty, which limits the pace of innovation. Furthermore, even if there is an existing runtime call these frameworks can use, it often does not offer optimal performance for a user's particular network architecture and dataset, missing optimizations between operators as well as optimizations that can be done knowing the size and shape of data. Our contributions include (1) a language close to the mathematics of deep learning called *Tensor Comprehensions*, (2) a polyhedral Just-In-Time compiler to convert a mathematical description of a deep learning DAG into a CUDA kernel with delegated memory management and synchronization, also providing optimizations such as operator fusion and specialization for specific sizes, (3) a compilation cache populated by an autotuner. In particular, we demonstrate the suitability of the polyhedral framework to construct a domain-specific optimizer effective on state-of-the-art deep learning models on GPUs. Our flow reaches up to  $4\times$  speedup over NVIDIA libraries on kernels relevant to the Machine Learning Community, and on an actual model used in production at Facebook. It is integrated with mainstream frameworks Caffe2 (production-oriented), PyTorch (research-oriented), through the ATen asynchronous tensor library.

### 1 Introduction

Deep neural networks trained with back-propagation learning [52] are a method of choice to solve complex problems with sufficient data. Recently, GPU-accelerated algorithms have excelled in this area [73, 21, 50]. Popular computation graph engines [81, 24, 17, 1] offer high-level abstractions for optimizing and executing deep neural networks expressed as graphs of tensor operations. These frameworks make transparent use of GPUs and other hardware accelerators for low power or low latency [55, 44] and are often implemented as an abstraction over highly-optimized routines for individual operators. While these operators are sufficient for many applications, they fall short in a number of instances where the computation does not fit the supported library calls. Consider a researcher who wants to develop a novel type of layer or network architecture. She must develop a custom operator, often at a high engineering cost and performance penalty. Furthermore, even when it is possible to represent a given network with library calls, they often miss peak performance for two reasons: missed optimizations across operators, and no tuning for every combination of size, shape and data flow encountered in Machine Learning (ML) [83].

Alone, computation graphs in such frameworks are too abstract to capture essential refinements and lowering steps required for efficient use of hardware accelerators, unless the operators perfectly fit a pre-optimized set of library functions. The parallel execution of individual layers and the memory layout of individual tensors varies greatly depending on data size and shape, upstream and downstream computations, and specific hardware features.

#### 1.1 Motivations

These observations have pushed for an active library [85, 8] or built-to-order (BTO) approach [9], in which library code is specialized and generated on-demand. However, this approach does not quite solve the problem as tuning library kernels in isolation misses context-dependent opportunities and creating a library that covers all combinations of individual kernels is infeasible.

This has led to the creation of domain-specific languages such as Halide [72], which has been successful in imaging due to its ability to fuse large pipelines without obfuscating the underlying algorithm. However when using Halide on the GPU, all scheduling transformations must be manually specified, and achieving high performance with the right combination of them is beyond the ability of most users.

More recent deep learning compilers such as XLA [36] and Latte [82] seem to be the ideal solution to this problem: they combine operators from computation graphs, allowing for optimizations across operators as well as optimizations that take advantage of data size. Yet, so far, the expected performance levels have not been met on GPU targets. The transformation language of these frameworks does not seem to be able to represent complex scheduling and mapping transformations which are often crucial to GPU targets with partitioned memory architectures.

To remedy this, an effective programming language for computation graph engines must simultaneously address the two following challenges:

- ensure that abstraction not only enhances programmer productivity but also enables the compiler and its supporting execution environment to eliminate concerns irrelevant to the target platform, to refine the code through intermediate representations closer to the machine, and to automatically explore a wide optimization space. In other words, the system must be able to offer "abstraction without regret" [76, 22] while conveying rich semantical information available at compilation time;

- select appropriate intermediate representations and optimization algorithms that deal with deep parallelism and memory hierarchies, as well as hardware features such as vector instructions and special-purpose memory.

### 1.2 Contributions

We present a novel domain-specific flow capable of generating highly-optimized kernels for tensor expressions, leveraging optimizations across operators and optimizations that take into account the size and shape of data. We address the first challenge through the design of Tensor Comprehensions (TC), a domain-specific language whose syntax is both concise and expressive and whose

semantics allows for efficient memory management and mapping to complex parallel platforms. We address the second challenge by specializing a polyhedral intermediate representation and its compilation algorithms to the domain of deep learning, providing it with a dedicated autotuner. The polyhedral framework of compilation emerged as a natural candidate to design a versatile intermediate representation and optimization flow satisfying the needs of the domain and target hardware. The polyhedral framework has demonstrated strong results in domain-specific optimization [59, 7, 3], expert-driven metaprogramming [32, 15, 4], libraries of high-level transformations of control flow and storage [48], and embedding of third-party library code [49], and automatic generation of efficient code for heterogeneous targets [5, 54, 66, 88, 3, 95].

In this report, we present the following contributions:

- Tensor Comprehensions (TC): a high-level language to express tensor computations arising in ML with a syntax generalizing the Einstein notation. It supports shape and size inference, flexible element-wise syntax with both named and positional parameters. It has conciseness and safety advantages, avoiding off-by-one errors while also allowing layout transformations and specialization.

- An end-to-end compilation flow capable of lowering tensor comprehensions to efficient GPU code. It delivers strong baseline performance for custom operators and remains competitive with vendor libraries on standard ones. The former is essential to reducing the technical debt on vendor libraries, enabling ML researchers to explore a wider field of architectures and layers in production-like scenarios.

- A collection of polyhedral compilation algorithms with a specific domain and target orientation. Unlike general-purpose parallelizing compilers, we primarily optimize for reduced launch and synchronization overhead through kernel fusion and also favor multi-level parallelism and promotion to deeper levels of the memory hierarchy.

- An autotuning framework that takes advantage of Just-In-Time (JIT) compilation and code caching. It includes specialization for non-standard sizes, eliminating control and address generation logic, and takes ownership of all optimization knobs from the ML framework to the code generator.

- Integration into two common ML frameworks (PyTorch [71] and Caffe2 [37]). In principle our system is general enough to be integrated into other ML frameworks.

For our initial system, we focus on the generation of CUDA code because NVIDIA GPUs dominate the hardware landscape for training deep neural networks. We believe our approach applies to other types of heterogeneous nodes with shared or partitioned memory.

The report comes with supplementary material labeled as Section A, covering background on polyhedral compilation and deep learning frameworks, implementation details and further experimental methodology. I

# 2 Related Work

Despite decades of progress in optimizing and parallelizing compilation, programmers of computationally intensive applications complain about the poor performance of optimizing compilers, often missing the peak achievable performance by orders of magnitude. Among the reasons for this state of affairs, one may cite the complexity and dynamic behavior of modern processors, domain knowledge required to prove optimizations' validity or profitability being unavailable to the compiler, program transformations whose profitability is difficult to assess, and the intrinsic difficulty of composing complex transformations, particularly in the case of computationally intensive loop nests [23, 25, 32, 15, 48, 4].

Several contributions have successfully addressed this issue, not by improving a general-purpose compiler, but through the design of application-specific program generators, a.k.a. active libraries [85]. Such generators often rely on feedback-directed optimization to select the best generation strategy

<sup>&</sup>lt;sup>1</sup>The report is meant to be easily accessible to a reader familiar with parallelizing compilation, performance tuning for GPUs, and a basic knowledge of the polyhedral framework, tensor algebra and convolution operations.

[77], as popularized by ATLAS [92] for dense matrix operations—and more recently BTO [9]—and FFTW [31] for the fast Fourier transform. Most of these generators use transformations previously proposed for traditional compilers, which fail to apply them for the aforementioned reasons. The SPIRAL project [69] made a quantum leap over these active libraries, operating on a domain-specific language (DSL) of digital signal processing formulas. Compilers for DSLs typically rely on domain-specific constructs to capture the intrinsic parallelism and locality of the application. Using such an approach, DSL compilers such as Halide [72] for image processing show impressive results. Its inputs are images defined on an infinite range, while TC sets a fixed size for each dimension using range inference. This is better suited to ML applications, which mostly compute on fixed size tensors with higher temporal locality than images; it is also less verbose in the case of reductions and does not carry the syntactic burden of pre-declaring stage names and free variables (Halide needs this as a DSL embedded in C++). OoLaLa [53] takes a similar approach for linear algebra, and TACO [46] and Simit [47] use a notation similar to that of TC, but generate sparse matrix code for numerical solvers.

Following this trend in the context of deep neural networks, we not only design yet another DSL and compiler but propose a more generic code generation and optimization framework bringing together decades of research in loop nest optimization and parallelization for high-performance computing. We also design the domain language to cover a variety of existing and emerging machine learning models. Our framework automates a combination of affine transformations involving hierarchical tiling, mapping, shifting, fusion, distribution, interchange, on either parametric or fully instantiated problems, that are not accessible to Halide [72, 57], Latte [82] or XLA's [36] representations of tensor operations.

The polyhedral framework is a powerful abstraction for the analysis and transformation of loop nests, and a number of tools and libraries have been developed to realize its benefits [28, 12, 88, 11, 95], including components for production compilers such as GCC (Graphite) and LLVM (Polly). Polyhedral techniques have also been tailored for domain-specific purposes. State of the art examples include the PolyMage [59] DSL for image processing pipelines and the PENCIL approach to the construction of parallelizing and compilers for DSLs [3, 7]. Interestingly, some optimization techniques derived from PolyMage crossed over from polyhedral representations into Halide's recent automatic scheduler [58]. Our compiler implements optimizations specific to the long, non-uniform reuse patterns and deeply nested loops of deep learning models; these heuristics are not available in Halide and variants [59, 57].

Back to deep learning frameworks, TC shares several motivations with Latte [82], including a high level domain-specific language and an end-to-end flow. TC provides an element-wise access that is just as expressive when implementing custom layers, but unlike Latte it is more concise thanks to type and shape inference, safer regarding static bound checking and graph connectivity, and more flexible by decoupling indexing from representation and layout choices (e.g., sparse layers). In addition, our framework implements more complex scheduling and mapping transformations than Latte, some of which are essential to GPU targets with partitioned memory architectures. Unlike Latte, it is also designed as a JIT compilation library for seamless integration with deep learning frameworks.

Like tensor comprehensions, XLA [36] provides automatic shape and size inference, it may operate "in process" as a JIT compilation library, and it integrates into a production deep learning framework (TensorFlow, Caffe2 [37]). XLA shares many motivations with Latte, with a focus on integration and completeness of functionality rather than on the complexity of the optimizations and mapping strategies. Most of our design and algorithmic contributions would naturally fit XLA, except for the following: TC remains independent from a specific computation graph framework while preserving tight integration with production frameworks; we did not use an embedded DSL approach—keeping C++ as an interface for implementing optimization strategies only—isolating the user from complexity and debugging hurdles of embedded DSLs.

Most recently, R-Stream·TF [67] was presented as a proof-of-concept adaptation of the R-Stream polyhedral compiler to the automatic optimization of TensorFlow operators. Similarly to our approach, the generated code is wrapped as a custom operator of TensorFlow. The tool takes a computation graph as input and partitions it into subgraphs amenable to tensor fusion, contraction and layout optimization. R-Stream·TF also leverages the broadcast semantics of TensorFlow to maximize the operator's polymorphism w.r.t. input tensor dimension and shapes. This makes R-Stream·TF very aggressive in terms of static memory management and kernel partitioning. We made the

more pragmatic choice of leaving most of these decisions to the level of tensor algebra, allowing a domain-specific optimizer or ML expert to rewrite declarative comprehensions into capacity- and layout-optimized ones. On the contrary, TC is more ambitious in its domain-specialization of affine scheduling and mapping, aiming for the generation of a single accelerated kernel, with heuristics adapted to the high dimensionality and non-uniform, long reuse patterns of neural networks. The lack of algorithmic detail in the paper does not let us compare those affine transformation heuristics at the time of writing.

# 3 Tensor Comprehensions

We provide a language for expressing element-wise computations of tensors using *tensor comprehensions*.

Tensor Comprehensions (TC) are a notation for computing on multi-dimensional arrays that borrows from the Einstein notation (a.k.a. summation convention):

- 1. index variables are defined implicitly by using them in an expression and their range is inferred from what they index;

- 2. indices that appear on the right of an expression but not on the left are assumed to be reduction dimensions;

- 3. the evaluation order of points in the iteration space does not affect the output.

Let us consider matrix-vector product as a simple example of a tensor comprehension with two statements:

```

def mv(float(M,K) A, float(K) x) \rightarrow (C) {

C(i) = 0

C(i) += A(i,k) * x(k)

}

```

This defines the function mv with A and x as input tensors and C as output. The statement introduces two index variables 'i' and 'k'. Variables not defined anywhere, implicitly become index variables. Their range is inferred based on how they are used in indexing (see below); here we will discover i = [0,M), and k = [0,K). Because k only appears on the right-hand side, stores into C will reduce over k with the reduction operator +. Reductions can occur across multiple variables, but they all share the same kind of associative and commutative operator (e.g., +=) to ensure that evaluation order does not affect the computed value (e.g., composition of min and max do not commute,  $\min(\max(f(\cdot))) \neq \max(\min(f(\cdot)))$ ).

Intuitively, a tensor comprehension may be thought of as the *body* of a loop whose control flow is inferred from context. The equivalent C-style pseudo-code is:

```

tensor C({M}).zero(); // O-filled single-dim tensor

parallel for (int i = 0; i < M; i++)

reduction for (int k = 0; k < K; k++)

C(i) += A(i,k) * x(k);</pre>

```

Importantly, the nesting order (i then k) is arbitrary: the semantics of a tensor comprehension is always invariant by loop permutation.

TC allows in-place updates, but preserves a functional semantics that is atomic on full tensors: the semantics is to *read RHS expressions in full before assigning any element on the LHS*. This specification is important in case the LHS tensor also occurs in RHS [30]: the compiler is responsible for checking the causality of in-place updates on element-wise dependences. We currently implement a simple syntactic check, allowing only in-place updates on pointwise definitions and tensor contractions. When this check fails, the compiler rejects the program due to liveness interference; for example, any in-place transposition a(i,j) = a(j,i) is incorrect (unless the range is empty or a single element), while a(i,j) = b(j,i) is a valid transposition. Of course, this explicit reuse and atomic update semantics does not preclude other scheduling and storage mapping decisions by the compiler, as long as these preserve the element-wise dependences of the TC. This mixed declarative-imperative design of TC is inspired from Lush [13].

```

\begin{array}{lll} \textbf{def sgemm}(\texttt{float a, float b,} \\ & \texttt{float}(\texttt{N},\texttt{M}) \texttt{ A, float}(\texttt{M},\texttt{K}) \texttt{ B}) \rightarrow (\texttt{C}) \texttt{ \{} \\ \texttt{C}(\texttt{i},\texttt{j}) &= \texttt{b} * \texttt{C}(\texttt{i},\texttt{j}) & \texttt{\# initialization} \\ \texttt{C}(\texttt{i},\texttt{j}) &+= \texttt{a} * \texttt{A}(\texttt{i},\texttt{k}) * \texttt{B}(\texttt{k},\texttt{j}) & \texttt{\# accumulation} \\ \texttt{\}} \end{array}

```

Figure 1: Tensor Comprehension for the sgemm BLAS

Reductions in TC are often initialized with the reduction operator's neutral element; we provide a short-cut for an *initializing reduction*, appending '!' to the reduction symbol, i.e., '+=!' instead of '+='. Here is a one line definition of the matrix-vector product:

```

def mv(float(M,K) A, float(K) x) \rightarrow (C) {

C(i) +=! A(i,k) * x(k)

}

```

Using these simple properties, common machine learning kernels can be written in just a few lines. For instance, Figure 1 shows the SGEMM function of the BLAS library. General tensor contractions can be expressed along the same lines. A fully connected layer followed by a rectified linear unit takes the form of a transposed matrix multiplication initialized to a broadcast bias term and followed by pointwise clamping (i.e., fmaxf with 0):<sup>2</sup>

Here we chose to reuse the out tensor across all comprehensions, indicating the absence of temporary storage.

A 2-D convolution is similarly simple, its reduction is initialized to 0 (note the use of +=!):

```

\begin{array}{lll} \operatorname{def} & \operatorname{conv2d}(\operatorname{float}(B,\operatorname{IP},\operatorname{H},\operatorname{W}) & \operatorname{in}, \\ & & \operatorname{float}(\operatorname{OP},\operatorname{IP},\operatorname{KH},\operatorname{KW}) & \operatorname{weight}) \to (\operatorname{out}) \ \left\{ & \operatorname{out}(b,\operatorname{op},h,\operatorname{w}) \right. += ! & \operatorname{in}(b,\operatorname{ip}, \ h + \operatorname{kh}, \ \operatorname{w} + \operatorname{kw}) \\ & & * \operatorname{weight}(\operatorname{op},\operatorname{ip},\operatorname{kh},\operatorname{kw}) \\ \left. \right\} \\ \end{array}

```

with reduction dimensions kh, kw. A max pooling layer is:

```

def maxpool2x2(float(B,C,H,W) in) → (out) {

out(b,c,i,j) max=! in(b,c, 2 * i + kw, 2 * j + kh)

where kw in 0:2, kh in 0:2

}

```

In the case of max pooling, the indexes kw and kh, which determine how many entries to pool over, are under-constrained since they are not inferable from any input tensors and the range inference procedure emits an error when no further information is provided about these indices. So we provide a where annotation to inform the inference algorithm of the intended ranges of these variables and let it infer the remaining ranges from context.

Subscript expressions can be any affine function of iterators, or subscript-of-subscript expressions, and combinations thereof. The latter capture data-dependent accesses such as a gather operation:

```

\frac{\text{def gather(float(N) X, int(A,B) I)} \rightarrow \text{(Z) } \{ \\ \text{Z(i,j)} = \text{X(I(i,j))} \}

```

<sup>&</sup>lt;sup>2</sup>For historical reasons related to the expression of element-wise linear algebra in the context of neural networks, the expression in matrix form often involves transpositions. TC lifts that impedance mismatch and makes it non-surprising: the tensor layout and sizes must match what is expected from the indexing expression.

TC closely matches an algorithmic notation. This is not true of today's prominent frameworks where most operators are defined as black-box functions. The design of TC makes it easy to experiment with small layer variations, while preserving a concise, in-place expression. For instance, recently, strided convolutions have become popular in image classification [93]. With tensor comprehensions, a strided convolution is easily created as a tweak on convolution, here is a convolution strided by sh along h and sw along w:

```

\begin{array}{lll} \text{def sconv2d(int sh, int sw, float(N,C,H,W) I,} \\ & & \text{float(F,C,KH,KW) W, float(F) B)} \rightarrow \text{(0) } \{\\ \text{O(n,f,h,w)} &= \text{B(f)} \\ \text{O(n,f,h,w)} &+= \text{I(n,c, sh * h + kh, sw * w + kw)} \\ & & \text{* W(f,c,kh,kw)} \\ \} \end{array}

```

Note that efficient implementations of sconv2d can take advantage of partial evaluation for the frequent case where sh and sw are constant, resulting in affine subscript expressions. This is another advantage of JIT compiling TC.

### 3.1 Range Inference

Tensor comprehensions are concise because most of the time loop ranges are inferred from context. Similar to the inference of polymorphic data types, the inference algorithm aims to accurately infer the range based on usage patterns. It is not always possible however, due to non-affine expressions or under-constrained problems—see e.g., max pooling. TC needs additional annotations for such cases.

Iteration variables are always non-negative. Unless specified otherwise in a where clause, each iteration variable is assumed to start at 0.

Inference is computed from input arguments to output tensors, setting up a constraint-based analysis problem across all the affine array accesses in a TC function. We initially looked for a very general setting of this problem, with an inference algorithm relying on Presburger arithmetic as implemented in polyhedral libraries [87]. Yet, to program productively, one must be able to mentally emulate the written code on the abstract machine defined by the language semantics. If this requires more thought than writing explicit loops would, our language design has failed. With this in mind, we eschew heavy-duty mathematical tools, and take a more straightforward approach for the sake of usability. We infer ranges only in cases where we feel they are obvious, and require explicit annotation elsewhere. We intend to fine-tune this boundary in the future depending on what users find surprising.

To find a good first approximation, we infer rectangular ranges that are as large as possible without reading out of bounds on the inputs. If there is more than one way to do this, we throw an error and require explicit annotation using a 'where' clause.

This rule is sufficient to understand the sgemm case above. Maximizing the range of i gives it the range of the number of rows of A. Similarly maximizing the range of j gives it the range of the columns of B. k is used twice, so making k as large as possible gives it the lesser of the number of columns of A and the number of rows of B. These in turn are constrained to be equal by the type signature of the function (they are both K).

Now consider a simple 1-D convolution:

There are multiple ways in which we could maximize the ranges of i and x. If we first maximize i, we might say that it ranges over the entirety of I. This forces x to take on a single value only, which will not result in the output one expects from a convolution, as it ignores most of the kernel! If we first maximize x, so that it ranges over the entirety of K, then in order to not read out of bounds the range of i must be smaller, and we get an output that is slightly smaller than the input. This is the behavior we prefer.

In order to make this unambiguous without requiring explicit annotation in this simple case, range inference proceeds in rounds. We maintain a set of unresolved variables. Initially, this set contains all variables not constrained with an explicit where clause. In each round, we consider

all the tensor argument expressions that contain a single unresolved variable, and construct a boolean expression that states the access is not out-of-bounds. We then use tools from Halide (solve\_for\_inner\_interval) to find the maximal range for the variable that satisfies this condition, given the ranges of variables already resolved in previous rounds. If the variable was already constrained in this round by some other tensor access, we take the intersection of the inferred ranges.

For the stencil above, in the first round we ignore the expression I(i+x) because it contains multiple unresolved variables. We use the expression K(x) to deduce a range for x. In the second round, I(i+x) now contains a single unresolved variable, and we use the already-inferred range of x to deduce a maximal range for i. In other words, the access K(x) constrains x to range from 0 to N-1, while the access I(i+x) constrains i+x to range from 0 to M-1, from which we deduce that i must satisfy the following constraint

$$\forall x \in [0, N-1], i+x \in [0, M-1],$$

which yields the final range of 0 to M-N for i.

Notice the  $\forall$  universal quantification on i, constraining the output tensor 0 to be uniformly defined across the entire domain from the exact same inputs in I. This differs from the approach taken in the Alpha language for systems of affine recurrent equations [51] where the domain scanned by x would be the projection of the triangular domain of (i,x) involving existential quantification:  $\{x\mid x\geq 0 \land \exists i\in [0,N-1],i+x\in [0,M-1]\}=[0,M-1].$  The semantical choice of quantifying iterators universally is derived from Halide; it guarantees that the shape of input tensors is always a (hyper-)parallelepiped, it is intuitive to ML experts and facilitates the generation of compact code, free of conditional control flow—unlike a more conventional projection semantics.

More complex examples involve intersecting successive rounds of inference over the same variables, and also ambiguous cases where no single rectangular shape can be derived from a more general set of constraints. The latter will not type-check and the compiler will request the insertion of a disambiguating where clause.

In addition, since memory management is externalized to a ML framework, the list of temporary tensors defined within a TC must be made explicit—with their shape and ranges; the range inference algorithm infers this list automatically. Finally, the inference algorithm can be formalized as a type and effect system [61], collecting constraints on index sets along the sequence of tensor definitions.

In its first release, TC does not support recurrent definitions such as those needed for the implementation of Recurrent Neural Networks (RNN).

Note that tensor indexing may involve any integer-valued expression, as long as it does not depend on the LHS tensor of the current statement. The compiler does its best at range inference and in the static verification that individual elements are defined only once in an imperatively-defined dimension; compilation fails in case range inference does not succeed and no where clause is there to provide the missing information.

#### 3.2 Data Layout Transformations

TC makes global data layout transformations significantly easier. The ML community has been heavily relying on such transformations by composing operations on tensor metadata in the form of a tuple of (dataPtr, offset, size[], stride[]) [9]. One of the main usage ML researchers have for such primitives is algorithmic tiling and hierarchical decompositions. The former has strong connections to data tiling and is now ubiquitous in the implementation of high-performance convolutions in the frequency domain to keep the memory footprint under control [83] or to fit to fast local memories [2]. The unfold operation in Lush [13] and Torch [24] perfectly matches implicit data tiling (i.e., without explicit memory copies), when there are no partial border effects. TC supports generalized tensor transpositions (i.e., applying an n-D permutation matrix where n > 2) and data tiling can be achieved by simply reshaping tensors and adjusting the TC index expressions. Range inference and checking guarantees such reshaping will always be consistent throughout a TC. Array-of-struct to struct-of-array conversions—and similar operations on short vectors—are available by-products: they are particular cases of dimension interchange and data tiling. At this time, data layout and TC transformations are left to the domain expert at source level, the TC inference procedure guarantees the expressions have the proper ranges. We will reevaluate this assumption in the future as we introduce automatic data layout transformations in TC.

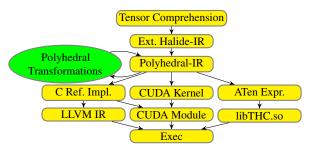

Figure 2: The JIT compilation flow lowers TC to Halide-IR, then to Polyhedral-IR, followed by optimization, code generation and execution

# 4 High-Level Workflow Description

Let us position our work in the context of deep learning frameworks such as TensorFlow, Caffe2 and PyTorch.<sup>3</sup>

TC expressions are first integrated into the ML framework as follows. We opted for an "in process" implementation, streamlining the interaction with computation graph engines and ML applications built on top of them, a unique feature for a fully-automated scheduling and mapping flow. We provide a thin API that translates the specific tensor object model to our own. Operator definitions are overridden to generate TC rather than the framework's backend implementation, as well as provide users the ability to write their own TC.<sup>4</sup> In this context, a single TC may correspond to a DAG of operators in the ML framework. This matching is currently done manually. Automatic DAG partitioning, matching and rewrites (like e.g., TensorRT [62]), informed by our compilation flow, are left for future work. The TCs are then JIT compiled as shown in Figure 2. In cases where the default backend implementation performs better, we fall back to the reference implementation.

Starting from a TC with specialized tensor sizes and strides,<sup>5</sup> we lower it to a parametric Halide expression.

In a prototype version of the system, Halide-IR was lowered to polyhedral representation via a translation to PENCIL [3] and then parsed using the pet [89] and isl [86] libraries. To reduce the impedance mismatch between IRs and to facilitate the propagation of semantical annotations, the flow evolved to lower Halide-IR directly to a polyhedral representation, bypassing the PENCIL intermediate language.

Similarly, we bootstrapped CUDA kernel generation in the original prototype from a modified version of the PPCG compiler [88]. The modifications included its usage as a library, for in-process, multi-threaded operation (see Section 5). When moving away from PENCIL, the functions of PPCG were reimplemented from the ground up, aiming for more modularity and compliance with a modern C++ environment.

Complementing this flow, an autotuner and a serializable compilation tightly interact with scheduling and mapping strategies to search the transformation space (see Section 6).

Additionally, we provide a simple "identity" polyhedral mapping option to generate a naive, readable, CUDA reference implementation that may be run and checked for correctness on a single GPU thread and shake off simple problems. We are planning a simple LLVM JIT compilation pass to make that reference implementation more generally usable on a CPU, but this is not yet implemented.

Lastly, we will provide a path to emit a series of library calls, a useful fallback to default implementations backed by CUDNN.

<sup>&</sup>lt;sup>3</sup>See Section A.1 for a brief introduction to these frameworks.

<sup>&</sup>lt;sup>4</sup>Section A.2 describes the programming interface for TC.

<sup>&</sup>lt;sup>5</sup>Our toolchain supports parametric specifications, yet we have found early specialization to be beneficial in driving profitability decisions during polyhedral scheduling.

# 5 Polyhedral JIT Compilation

The compiler bridges the impedance mismatch between the logical layout of high level tensor operations (dimension ordering) and the data format the polyhedral code generator expects (C99 arrays [3]). The lowering step ensures combinations of size and stride correspond to non-aliasing array and subarray syntax; it also ensures the absence of out-of-bounds access, analyzing access relations and inferred tensor ranges; it emits tensor declarations and reorder expressions to match the data model of the target language, i.e., row-major arrays.

Note that tensor specifications may feature input and output arguments aliasing for in-place computation and implicit conversion of tensors of higher dimension. We argue that such specifications should lead to multi-versioning and specialization for each aliasing scenario. Also, the semantics adopted by TC, building on range inference, differs from NumPy-style "broadcast" semantics adopted in some form or another by XLA, PyTorch and MXNet.<sup>6</sup> TC does not need such implicit syntactic sugar. For example, the TC corresponding to the so-called outer product matrix multiplication [p,q,r] matmul  $[1,s,r,t] \rightarrow [p,s,q,t]$  is simply:

```

def outerProductMM(float(P,Q,R) A, float(S,R,T) B) \rightarrow (0) { 0(p,s,q,t) +=! A(p,q,r) * B(s,r,t) }

```

One may further transform layouts and derive a QPTS version (named by the ordering of output dimensions) instead of PSQT if desirable.

Additional lowering steps include forward substitution of convolution expressions (storage/computation tradeoff), padding with zero, mirroring and clipping.

The *polyhedral framework* offers a state-of-the-art internal compiler representation of loop-based programs that are "mostly regular" [29]. In its most basic form, it describes arithmetic expressions surrounded by loops and branches whose control flow can be determined statically. Hence the polyhedral framework is said to operate on *static control parts* (SCoP) of the program. More specifically, loop bounds and branch conditions are affine expressions of outer loop iterators and statically unknown constant values that are treated symbolically and referred to as *parameters*. Computation is described using arithmetic expressions on array elements with the same restrictions on subscripts as on loop bounds. Extensions exist to handle irregularities through over-approximation [10] or user-defined annotations [3]. Despite its deceiving apparent simplicity, the framework captures large classes of computation-intensive codes, it is parametric on domain and array sizes, and more expressive than domain-specific representations such as Halide's.

This work demonstrates that the polyhedral framework is particularly well suited for deep neural networks, associated with large and deeply nested loops with long dependence chains and non-uniform or all-to-all patterns—arising from fully connected layers and tensor contractions and transpositions. These features push the optimization problem into a different heuristic space than Halide's for image processing, and a much wider space than linear algebra alone.

We use the *named relation notation* introduced in iscc [87] for unions of relations where tuples of iterators are guarded with syntactic identifiers [68]. The reader unfamiliar with polyhedral compilation—iteration domains, affine access and dependence relations, scheduling and polyhedral code generation—may refer to Section A.3 in the supplementary material.

**Schedule Trees** Affine maps can be composed into *schedule trees* [90] to facilitate the communication of properties from the high-level language (here, TC) to the downstream optimizer and to attach target-specific information along the way (e.g., SPMD thread-relative induction as in CUDA, synchronization, data transfer instructions [88, 3]). Schedule trees introduce specific node types. A *band node* defines a *partial* execution order through one or multiple piecewise affine functions defined over iteration domains. The name refers to the notion of a *permutable schedule band*, a tuple of one-dimensional schedule functions that can be freely interchanged while preserving the semantics of the program. An affine function in a band is often referred to as a *band member* or a *schedule*

<sup>&</sup>lt;sup>6</sup>Broadcasting is a set of non-trivial rules that allow implicit conversion between tensors of different dimensions. It enables certain tensor operations even when an appropriate library implementation does not exist for those non-conforming shapes. It carries its baggage and ambiguities when dealing with higher dimensional tensor contractions, as demonstrated in the TensorFlow Github issue #5523.

dimension. A collection of filter nodes partitions the iteration space, binding its subtree to a subset of the iteration domain. They can be arranged into set or sequence nodes depending on whether the order of execution must be constrained for correctness or not (i.e., whether or not it corresponds to an #pragma omp sections). Context nodes provide additional information on the variables and parameters, e.g., tensor extents or GPU grid/block sizes; they may also introduce local scopes and parameters constant within a subtree, which is useful when mapping induction variables to block and thread identifiers in CUDA. Finally, extension nodes introduce auxiliary computations that are not part of the original iteration domain, which is useful for, e.g., introducing statements copying data to and from shared memory.

```

\begin{cases} \mathbb{S}(i,j) & | \ 0 \le i < N \land 0 \le j < K \} \\ \mathbb{T}(i,j,k) & | \ 0 \le i < N \end{cases}

\text{Domain} \begin{bmatrix} \{ \mathbf{S}(i,j) \mid 0 \leq i < N \land 0 \leq j < K \} \\ \{ \mathbf{T}(i,j,k) \mid 0 \leq i < N \land 0 \leq j < K \land 0 \leq k < M \} \end{bmatrix}

Domain

\wedge 0 \le j < K \wedge 0 \le k < M

Band  \begin{cases} \{ \mathbf{S}(i,j) & \rightarrow (i,j) \} \\ \{ \mathbf{T}(i,j,k) & \rightarrow (i,j) \} \end{cases}

\rightarrow (i, j)

Sequence

Filter{S(i, j)}

Sequence

\mathrm{Band}\{\mathtt{S}(i,j)\to(i,j)\}

Filter{S(i, j)}

Filter\{T(i,j,k)\}

Filter\{T(i, j, k)\}

\operatorname{Band}\{\mathtt{T}(i,j,k)\to(i,j,k)\}

\operatorname{Band}\{\mathtt{T}(i,j,k)\to(k)\}

(a) canonical sgemm

(b) fused

\{\mathtt{S}(i,j) \quad | \ 0 \leq i < N \land 0 \leq j < K\}

\{ S(i,j) \mid 0 \le i < N \land 0 \le j < K \}

Domain

\{\mathtt{T}(i,j,k) \mid 0 \le i < N

\{\mathtt{T}(i,j,k) \mid 0 \leq i < N \land 0 \leq j < K \land 0 \leq k < M\}

Domain

\wedge 0 \le j < K \wedge 0 \le k < M

\begin{bmatrix} \{\mathtt{S}(i,j) \\ \{\mathtt{T}(i,j,k) \end{bmatrix}

\rightarrow (32\lfloor i/32\rfloor, 32\lfloor j/32\rfloor)\}

Band

\rightarrow (32\lfloor i/32\rfloor, 32\lfloor j/32\rfloor)\}

\rightarrow (32[i/32], 32[j/32])\}

\{S(i,j)\}

Band

\{\mathtt{T}(i,j,k)

\rightarrow (32[i/32], 32[j/32])

Sequence

Band \begin{bmatrix} \{ \mathbf{S}(i,j) \\ \{ \mathbf{T}(i,j,k) \end{bmatrix}

\rightarrow (i \mod 32, j \mod 32)

Filter{S(i, j)}

\rightarrow (i \mod 32, j \mod 32)

\mathrm{Band}\{\mathtt{S}(i,j)\to (i\bmod 32, j\bmod 32)\}

\operatorname{Filter}\{\mathtt{T}(i,j,k)\}

Sequence

Filter{S(i,j)}

\operatorname{Band}\{\mathtt{T}(i,j,k)\to (32\lfloor k/32\rfloor)\}

Band\{T(i, j, k) \rightarrow (k \mod 32)\}

Band\{T(i, j, k0 \rightarrow (i \mod 32, j \mod 32)\}

Filter\{T(i, j, k)\}

Band\{T(i,j,k) \rightarrow (k)\}

(c) fused and tiled

(d) fused, tiled and sunk

Domain \left[ \begin{cases} \{ \mathbf{S}(i,j) \mid 0 \le i < N \land 0 \le j < K \} \\ \{ \mathbf{T}(i,j,k) \mid 0 \le i < N \land 0 \le j < K \land 0 \le k < M \} \end{cases} \right]

\begin{array}{l} \text{Context}\{0 \leq b_x, b_y < 32 \land 0 \leq t_x, t_y < 16\} \\ \text{Context}\{0 \leq b_x, b_y < 32 \land 0 \leq t_x, t_y < 16\} \\ \text{Filter} \end{array}   \begin{array}{l} \{S(i,j) \mid i - 32b_x - 31 \leq 32 \times 16 \lfloor i/32/16 \rfloor \leq i - 32b_x \land \\ j - 32b_y - 31 \leq 32 \times 16 \lfloor j/32/16 \rfloor \leq j - 32b_y \land \\ \{T(i,j,k) \mid i - 32b_x - 31 \leq 32 \times 16 \lfloor i/32/16 \rfloor \leq i - 32b_x \land \\ \end{bmatrix}

\begin{array}{c} j - 32b_y - 31 \leq 32 \times 16 \left[ j/32/16 \right] \leq j - 32b_y \\ \rightarrow (32 \lfloor i/32 \rfloor, 32 \lfloor j/32 \rfloor) \} \end{array}

\begin{bmatrix} \{ \mathtt{S}(i,j) & \rightarrow (32\lfloor i/32 \rfloor, 32\lfloor j/32 \rfloor) \} \\ \{ \mathtt{T}(i,j,k) & \rightarrow (32\lfloor i/32 \rfloor, 32\lfloor j/32 \rfloor) \} \end{bmatrix}

Band

Sequence

Filter{S(i,j)}

Filter \{S(i,j) \mid (t_x - i) = 0 \mod 16 \land (t_y - j) = 0 \mod 16\}

\operatorname{Band}\{\mathbf{S}(i,j) \to (i \bmod 32, j \bmod 32)\}

Filter\{\mathbf{T}(i,j,k)\}

Band\{T(i, j, k) \to (32|k/32|)\}

\mathrm{Band}\{\mathtt{T}(i,j,k)\to (k \bmod 32)\}

Filter \{T(i, j, k) \mid (t_x - i) = 0 \mod 16 \land (t_y - j) = 0 \mod 16\}

Band\{T(i, j, k) \to (i \mod 32, j \mod 32)\}

(e) fused, tiled, sunk and mapped

```

Figure 3: Optimization steps for sgemm from Figure 1

A *canonical* schedule tree for a TC is defined by an outer Sequence node, followed by Filter nodes for each TC statement. Inside each filtered branch, Band nodes define an identity schedule with as many one-dimensional schedule functions as loop iterators for the statement. Implicit loops form a permutable band as per TC semantics. Figure 3.a shows the canonical schedule tree for the sgemm TC—declaration of parameters  $(N, M, K) \rightarrow \{\dots\}$  is omitted hereinafter for brevity.

One recognizes a 2-D nest for the initialization statement followed by a 3-D nest for the update statement. The schedule can be either parametric in input sizes, or have extra context information on the tensor sizes. In cases where Band nodes do not define an injective schedule, the statement instances are scheduled following the lexicographical order of their domain coordinates. Program transformation in the polyhedral model involves defining a different schedule, which corresponds to a different (partial or total) order of traversing the iteration domain. For example, observing that the C tensor is reused between two nests, one can construct the schedule in Figure 3.b to leverage access locality and improve performance. This tree features an outer band node with i and j loops that became common to both statements, which corresponds to *loop fusion*. The sequence node ensures

that instances of S are executed before respective instances of T enabling proper initialization. The second band is only applicable to T and corresponds to the innermost (reduction) loop k. Additionally, the tree introduces a Context node to state the assumptions about the values of parameters.

**Out-of-bounds accesses** The polyhedral model allows for relational encoding of tensor accesses. Composing those with the iteration domains expressed as sets allows for computing the set of all accessed tensor elements, i.e., the statement's footprint, and for checking whether it fits the (specified or inferred) tensor sizes. In particular, access relations enable the detection of out-of-bounds accesses. Elements that belong to the footprint  $\mathcal{F} = \mathcal{D}.\mathcal{A}$ , but not to the set of tensor elements  $\mathcal{T}$ , inferred from the tensor shapes, correspond to out-of-bounds accesses. Hence,  $(\mathcal{D}.\mathcal{A}) \setminus \mathcal{T} = \emptyset$  is a condition for the absence of out-of-bounds accesses.

## 5.1 Polyhedral Transformation and Mapping

When targeting a parallel architecture, program transformations involve a change of schedule and also a mapping strategy; these must respect the dependences while optimizing for target-specific properties. Beyond guaranteeing the validity of the transformation, dependences can be used to expose parallelism (independent instances can be executed in parallel) or to improve data access locality (dependent instances executed close in time). Several efficient scheduling algorithms exist, focusing on a combination of parallelism, locality and vectorization [91, 12, 95, 84, 65]. Our transformation engine is based on four components:

- 1. core polyhedral scheduling is provided by *isl*, which automatically optimizes for (outer) loop parallelism and locality; we tuned the affine scheduling heuristic towards folding a complete TC program into a single GPU kernel;

- 2. the schedule is further tiled to facilitate the mapping and temporal reuse on the deep parallelism and memory hierarchy of GPUs [91];

- mapping to GPUs borrows from algorithms previously implemented in PPCG [88], with additional extensions to support the more complex and imperfectly nested structures appearing in ML kernels;

- 4. memory promotion deals with explicit data transfers to and from shared and private memory spaces. These components and the TC-specific extensions are detailed below.

### 5.2 Scheduling

The core part of the *isl* scheduler iteratively solves integer linear programming problems to compute piece-wise affine functions that form schedule bands. It also ensures that these bands are permutable and can be further tiled. Internally, it builds a data dependence graph (DDG) where nodes correspond to statements and edges express dependences between them. Each edge is annotated with a set of "typed" dependence relations. The *isl* scheduler [91] is designed for better scalability since integer linear programming has exponential complexity in the worst case. In particular, it introduces the *affine clustering* technique that is based on computing the schedule bands separately for individual strongly-connected components of the DDG and then clustering these components iteratively and scheduling with respect to each other. Clustering not only decreases the size of the linear problems the scheduler has to solve, but also serves as a basis for *isl*'s loop fusion heuristic.

We extended the *isl* scheduler to provide the caller with a more fine-grained control over the scheduling process. For affine transformations, the user can supply additional arbitrary constraints to be inserted in the linear program. For clustering, the user can supply a decision function for pairwise dependence graph component combination, after it was demonstrated to be valid by the scheduler. These configuration points serve as a basis for *scheduling strategies*. With these strategies, affine transformations can be restricted to: (1) non-negative schedule coefficients and/or, (2) non-skewing transformations (i.e., loop interchange and shifting). Clustering decisions allow for control over the conventional minimum and maximum fusion targets, and additionally, maximum fusion that preserves at least three nested parallel loops (to be mapped to CUDA blocks and threads). Scheduling strategies can be configured and selected through the autotuning process. In all cases, we enforce that a single GPU kernel is generated.

### 5.3 Imperfectly Nested Loop Tiling

Loop tiling is implemented as a separate step after the scheduling took place and performed as a schedule tree transformation. Essentially, it converts a permutable schedule band into a chain of two bands with the outer band containing tile loops and the inner band containing point loops with fixed trip count. This can be seen as a conventional strip-mine and sink transformation. For example, Figure 3.c shows the schedule tree for the fused and tiled sgemm.

In addition to conventional loop nest tiling, the schedule tree representation allows a tiling of imperfectly nested loops. The technique is based on the following observation: if a loop does not carry dependences (i.e., is parallel), it can be sunk below any other loop. In valid schedules, all dependences are carried (or satisfied) by some loop, along which they feature a positive distance. A dependence is only violated if it has a negative distance along some loop *before* it is carried by another loop [45]. Parallel loops do not carry dependences by definition and therefore do not affect dependence satisfaction or violation. Therefore, imperfectly nested tiling is implemented by first tiling all bands in isolation and then sinking parallel point loops in the tree. During this process, the point band is replicated in each subtree below a sequence (or set) node and its schedule is updated so that it only contains relevant domain points.

The schedule tree for sgemm purposefully has two imperfectly nested bands. Dependence analysis shows that loops i and j are parallel. Therefore, we can tile them and sink the point loops below the band of the reduction k loop, resulting in the schedule tree in Figure 3.d. Innermost nested bands with point loops can be joined together into a single band after checking for permutability.

### 5.4 Mapping to Blocks and Threads

A schedule tree can also be used to represent the *mapping* to an accelerator, in particular a GPU with multiple blocks and threads. This operation is performed by associating certain schedule band members, and the corresponding loops, to thread or block indexes. Polyhedral code generator then omits the loops, if possible, and rewrites the index expressions accordingly. Our mapping algorithm is derived from the one originally designed for PPCG, where grid and block sizes are specified independently from tile sizes. Due to the semantics of blocks and threads, only parallel loops that belong to a permutable schedule band can be mapped. If point loops are mapped to threads, the ratio between tile sizes and blocks sizes controls the number of iterations executed by each thread. Note that tile sizes smaller than the block sizes lead to some threads not performing any computation, if it is the point loops of the tiling that end up getting mapped to threads.

We require the schedule tree to have at least an outermost band with outer parallel dimensions. Contrary to PPCG, which maps each of possibly multiple outer bands to both blocks and threads (after tiling), our mapping algorithm maps a single band to blocks in order to generate a single kernel as expected by ML frameworks, while mulitple bands can be mapped to threads. The parallel dimensions of the (single) outermost band are mapped to GPU blocks. In each schedule tree branch, the innermost permutable band, typically consisting of point loops, is mapped to GPU threads with the following restrictions. The number of mapped dimensions must be equal across branches. This may require mapping some thread dimensions to zero in some branches.

The mapping itself is performed by inserting special names, communicated to the code generator through a context node, and by associating them to band dimensions in filter nodes. For the matrix multiplication example, our mapping strategy produces the schedule tree in Figure 3.e. We introduced a context node in the schedule tree to indicate the effective sizes of the parameters as well as the grid and block sizes (denoted as  $b_x, b_y$  and  $t_x, t_y$ , respectively, standing for values potentially taken by blockIdx.xy and threadIdx.xy). This insertion is performed just-in-time, when the effective tensor sizes are known. Also pay attention to the Filter nodes referring to  $b_x, b_y, t_x$  and  $t_y$  parameters. These nodes express the *mapping* to the GPU.

## 5.5 Memory Promotion

We are interested in promoting parts of tensors into shared or private GPU memory. While the promotion decision is taken by a heuristic and the corresponding imperative code is generated at a later stage, schedule trees offer a convenient interface for attaching memory-related information. Memory promotion is based on the notion of *array tile*, a form of data tiling for software-controlled

local memories. It is a constant-size potentially strided block in the array that covers all elements accessed within a given (schedule) tile. We revisit and extend PPCG's support for memory promotion [88, 91].

Promotion of Indirectly Accessed Arrays. Our memory promotion approach also handles indirectly accessed arrays. Without loss of generality, consider the access 0 [1+Idx[i][j]][k]. We refer to 0 as outer array and to Idx as index array. In case of nested indirections, outer/index pairs are processed iteratively from innermost to outermost. While the values taken by the first index expression of the outer array are unknown statically, we can still cache them locally as shared\_0[1][i][j][k] = 0[1 + Idx[i][j]][k]. Because some values can be duplicated, indirect promotion is only possible if both the outer and the index arrays are only read, writing to them could result in different values that cannot be trivially merged. In general, we require the index array to have an array tile, i.e., only a fixed-sized block of it is accessed. When computing the array tile for the outer array, we ignore the indirect parts of the subscript (affine parts are treated as usual). We then introduce as many additional index expressions in the promoted outer array as there are in the index array. Extents of the array along these new dimensions correspond exactly to the array tile sizes of the index array. Hence an element of the promoted array contains a copy of the global array element that would be accessed with the given index array. Indirect subscripts are only used when copying from the global memory while all other accesses are rewritten in the code generation. In presence of multiple indirect index expressions that share subexpressions and have equal tile sizes along the corresponding dimensions, it is sufficient to introduce a single index expression in the promoted array for all identical subexpressions.

**Promotion Heuristics.** Directly accessed arrays are promoted to shared memory if there exists an array tile of fixed size, if individual elements are accessed more than once and if at least one of the accesses does not feature memory coalescing. The latter is visible from the access relation with the schedule applied to the domain: the last access dimension should be aligned with the schedule dimension mapped to x threads. For indirect arrays, the coalescing requirement is dropped because of the presence of additional long memory dependences that these cases entail. The total amount of shared memory being fixed, we apply a simple greedy heuristic and refuse promotion if the required amount of shared memory would overgrow the available amount.

# 5.6 Mapping to Registers

There are currently no plans to implement more complex register promotion strategies than those previously supported by PPCG. This is a temporary, pragmatic choice, based on the following observations:

- except in limited cases [69, 80], we have not seen empirical evidence that automatically generating low-level code from a high-level specification results in a significant performance gain over assembly; additionally modern assembly generators are now publicly available and re-targetable [26];

- generalizing and re-targeting register optimization passes to different architectures with multiple vector lengths, alignment constraints and patterns is no easy task;

- many different strategies exist which include (1) pipelining at the register level, (2) register rotation, (3) multi-buffering, (4) new ISAs with collective-style semantics [63], some of which are not even available without significant genuflections;<sup>7</sup>

- often such strategies are first implemented with intrinsics and assembly as a proof of concept and can be easily templated and reused with a tool like PeachPy [26].

Performance results are slightly impacted by this temporary status of the implementation. We also plan to rely on external library calls, e.g., for accelerating reductions.

$<sup>^7</sup>$ E.g., the mix of register banking, L-1 FPU operand reuse, and control code on Maxwell GPUs, reverse-engineered and exploited in MaxAS (https://github.com/NervanaSystems/maxas).

# 6 Autotuning and Caching

While polyhedral scheduling and mapping to GPUs is very cheap compared to training a neural network, it is far from usable in a traditional JIT setting. We take advantage of the mostly static structure of neural networks to cache and reuse the best results of the autotuned compilation pass of an operation/kernel under similar conditions (input shapes, target architecture, and optimization options). We exploit this reuse with a compilation cache.<sup>8</sup>

### 6.1 Compilation Cache

The compilation cache stores the generated CUDA or PTX code for a given TC. The generated code depends on the input shapes, the selected optimization options (e.g., tile sizes, loop fusion scheduling strategy, mapping decisions) and the constraints induced by the target GPU architecture (e.g., shared memory/register size, fraction of shared memory to use for occupancy purposes, etc...). Each cache entry key is therefore a tuple:

(TC, input, shapes, target, architecture).

For the purpose of caching we use a summarily templatized version of TC to make the key agnostic to name changes. Each cache entry holds the fastest known version. Before each kernel optimization the cache can be queried. On a cache miss, the regular JIT compilation flow is invoked. The cache is serialized to a protocol buffer interchange format [35] to enable persistence and reuse. To avoid long and unpredictable compilation and autotuning times, one may pre-populate the cache with reference implementations. Since the cache serializes to strings, we added the capability to inject entries into the cache to support particular cases of interest where low-level manual tuning helps (the experiments in the report do not make use of this). In the current implementation, the size of the compilation cache could potentially become cause for concern: for every operation, the number of input shapes and optimization options can be arbitrarily large. In practice, however, the number of operations of interest is limited (e.g., the total number of different operators in Caffe2 v0.8.0 is approximately 400) and the space of input shapes is very sparse. Further characterization of these statistics will be the subject of future work. Importantly, note that our whole pipeline is parametric and specialization can be injected at any point (or not injected at all). For the time being we choose to inject runtime sizes as early as possible in the polyhedral compilation flow (i.e., before polyhedral scheduling) because it eagerly propagates valuable information for scheduling, tiling, mapping and total elimination of non-loop control flow (in static cases). One good candidate for parametrization is the minibatch dimension. The minibatch dimension is usually mapped to CUDA grid dimensions. These grid dimensions are specified by the kernel launch call and can be changed without the need to generate a different version. A separate database which includes performance data for all versions is also maintained for use in autotuning. This will be useful when additional search techniques are implemented such as Bayesian hyperparameter search [78], multi-armed bandit optimization [64] or black-box optimization [34].

### 6.2 Autotuning

The autotuner interacts with the rest of the environment through the compilation cache, storing the best versions for later use. It includes the following steps, setting up:

- 1. a set of starting configurations that worked well for similar TCs, and a few predefined strategies for reference problems;

- 2. the tuning space dimensions and admissible values for ranges;

- 3. the type of search—currently a genetic algorithm or random.

The autotuner runs for a prescribed amount of time, updating the cache with better versions along the way. It uses genetic search [33] which operates on generations of candidate configurations. In each tuning step the candidates are compiled and profiled, then assigned a fitness value inversely

<sup>&</sup>lt;sup>8</sup>Note that in a traditional dynamic setting such as stack-RNNs, few parameters vary and it is not unreasonable to compile multiple versions; we can also relax any dimension to remain parametric (the polyhedral framework handles parametric control-flow).

proportional to their runtime. Each new candidate is bred through three parent uniform cross-over and also undergoes mutation with a low probability.

- 1. three parents are selected probabilistically based on their fitness, the higher the fitness the higher the selection chance;

- 2. each "gene", which corresponds to one tuning parameter, of the new candidate is randomly selected from the parents.

Every new candidate also undergoes mutation: there is a low probability that zero or more of its genes are assigned random values. This probability is called the mutation rate and it controls the exploration versus exploitation tradeoff.

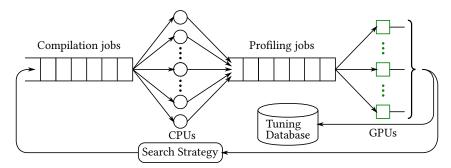

Autotuning evaluates 100s to 1000s versions for each kernel. Search strategies such as genetic algorithms require evaluating multiple candidates before each search step; we take advantage of this property by launching multiple compilation jobs in parallel with our generic multi-threaded, multi-GPU autotuner (see Figure 4). The search strategy enqueues multiple candidate configurations in the "Compilation Jobs" queue; the candidate configurations are compiled in parallel by multiple CPU threads. Whenever a compilation job is finished the result is enqueued in the 'Profiling Jobs' queue; each profiling job is evaluated on an available GPU; the profiling results are used to update the autotuning database and to generate the next set of candidates.

Figure 4: Multithreaded autotuning pipeline for kernels

A variety of kernel options are tuned:

- the search for tile, block, and grid sizes is narrowed to choices that help avoid tail effects; we consider both powers of 2 and integer ceil divisors of the problem sizes;<sup>9</sup>

- the bound on how many iterations can be unrolled on the bottom up paths from leaves to the root of the schedule tree; we consider powers of 2 up to 4096;

- discrete choices on fusion strategies and shapes of the admissible schedules, e.g., to prevent loop skewing and trade parallelism for locality;

- lower-level options such as shared or private memory usage and how aggressively to use those memory spaces in each block, which directly impacts GPU occupancy.

## 7 Examples And Performance Results

This section reports on the evaluation conducted on an earlier version used for a submission to the PLDI 2018 conference, relying on a modified version of the PPCG compiler [88]. The implementation and dependent packages in the public release of TC differ slightly, bypassing PENCIL [3] and reimplementing the necessary functions of PPCG.

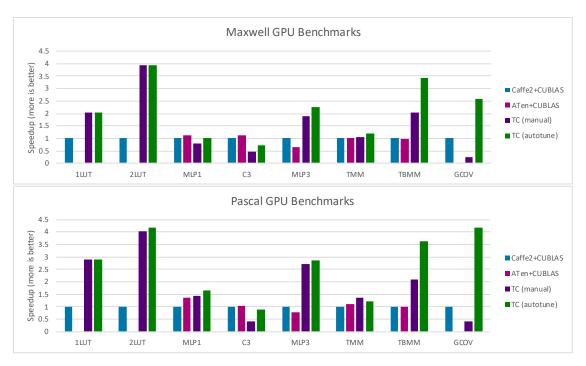

We consider two systems for all experiments:

$<sup>^9</sup>$ Indeed, it is common to see problem sizes close to a power of 2 (e.g., 130) for which it is often better to avoid launching an extra block at the cost of a slightly off tile or mapping size (e.g., 65); this brings up to 30% benefits on latency-bound kernels.

- 8 Maxwell nodes with 2 socket, 12 core Intel(R) Xeon(R) CPU E5-2680 v3 @ 2.50GHz, with 8 Tesla M40 GPUs and 12GB of memory each;

- 8 Pascal nodes with 2 socket, 14 core Intel(R) Xeon(R) CPU E5-2680 v4 @ 2.40GHz, with 8 Tesla P100-SXM2 GPUs and 16GB of memory each.

We use CUDA v8.0, CUBLAS v8.0.45, CUDNN v6.0.21, NVRTC v8.0. Note that with NVRTC v8.0 we experience an extra overhead of around  $15\mu s$  that can become more important than the kernel itself; this is understood to be reduced in NVRTC v9.0 [40]. When relevant, we discuss individual kernel performance measured with nvprof but always report all our numbers with the full CPU overhead, which includes a call to cudaDeviceSynchronize.

We report our baseline and best autotuned variant for every benchmark, together with the corresponding Caffe2 and ATen reference, when available. Note that Caffe2 is considered as one of the fastest ML frameworks.

The outputs are checked against the reference implementation. All benchmarks we report are run 1,000 times on the GPU. We report p0 (a.k.a. min), p50 (a.k.a. median) and p90 (90<sup>th</sup> percentile). The best autotuning results are serialized and saved in the compilation cache on disk. A subsequent validation procedure traverses the compilation cache for each example, selects the best mapping options and runs 1,000 iterations, checks against the reference implementation and logs the result. We autotune with 16 CPU threads and 8 GPUs per node. One full sweep of the genetic autotuner involves a population size of 100 over 25 generations and takes about 6 hours to complete. We find the bottleneck is often NVRTC compilation, in particular, we realized it acquires a global lock internally and can only process one kernel at a time.

Baseline mapping options are picked as "reasonable guesses": we did not spend time performing manual tuning but did not choose a trivially bad solution either. In particular, no iterative, user-involved, transform-inspect-evaluate loop is required and the polyhedral mapper already automates all decisions and also offers many different knobs that the autotuner can latch on. This should come as no surprise given the rich, 30-year history of the field of polyhedral compilation. We start our discussion with common kernels that are ubiquitous in ML workloads. We then show how TC fully automates the synthesis of CUDA kernels for research layers that do not yet have an existing HPC implementation. We conclude with a discussion of a model used in production.

Finally, in the context of ever increasing hardware computation capabilities, models that are bandwidth-bound today will increasingly shift towards the latency-bound regime. Specialization of kernel mapping close to that boundary crossing towards low-latency regimes is obtained automatically in this contribution.

We provide the baseline and best autotuner options in the supplementary material, and the final generated code where informative.

**Transposed Matrix Multiplication** In the context of deep learning, transposed matrix multiplication is ubiquitous:

```

\begin{array}{lll} \mbox{def } \mbox{tmm} (\mbox{float}(\mbox{M},\mbox{K}) \mbox{ A, float}(\mbox{N},\mbox{K}) \mbox{ B)} \rightarrow (\mbox{C)} \mbox{ \{} \\ \mbox{C}(\mbox{m},\mbox{n}) \mbox{ +=! } \mbox{A}(\mbox{m},\mbox{kk}) \mbox{ * B}(\mbox{n},\mbox{kk}) \mbox{ } \\ \mbox{B}(\mbox{n},\mbox{kk}) \mbox{ * B}(\mbox{n},\mbox{kk}) \mbox{ * B}(\mbox{n},\mbox{kk}) \mbox{ } \\ \mbox{B}(\mbox{n},\mbox{kk}) \mbox{ * B}(\mbox{n},\mbox{kk}) \mbox{ * B}(\mbox{n},\mbox{kk}) \mbox{ * B}(\mbox{n},\mbox{kk}) \mbox{ } \\ \mbox{B}(\mbox{n},\mbox{kk}) \mbox{ * B}(\mbox{n},\mbox{kk}) \mbox{ * B}(\mbox{n},\

```

At the largest problem sizes, our best autotuned version is  $4.2 \times$  (resp.  $3.4 \times$  on Pascal) *slower* than Caffe2 with CUBLAS. The reader should note this hints at the improvement potential of TC, although:

- 1. this is one of the most hand-tuned kernel in history and CUBLAS operates close to peak at large enough sizes;

- 2. we do not implement register tiling and advanced promotion schemes for now (see Section 5.6) hence performance is bound by shared memory bandwidth;

<sup>&</sup>lt;sup>10</sup>ATen—the asynchronous tensor library—currently wraps the Torch tensor library and is integrated with PyTorch. The ATen reference implementation is accessible from C++ and acts as a reasonable proxy for the expected PyTorch performance; but still not an apples-to-apples comparison.

<sup>&</sup>lt;sup>11</sup>It would be interesting to compare with Halide's autoscheduler. Unfortunately, it is not currently functional for GPUs.

## **Common and Research Kernels**

|               | (B, M, K, N) (nil, 128, 32)                                       |                              |                              | 256)                 | 56) (nil, 128, 1024, 1024) |                                |                                |                                | (nil, 128, 4096, 16384)          |                                    |                                    |                        | (500, 72, 26, 26        |                              | 6, 26)                       |

|---------------|-------------------------------------------------------------------|------------------------------|------------------------------|----------------------|----------------------------|--------------------------------|--------------------------------|--------------------------------|----------------------------------|------------------------------------|------------------------------------|------------------------|-------------------------|------------------------------|------------------------------|

|               |                                                                   | p0                           | p50                          | p90                  | p0                         | p50                            | р9                             | 0                              | p0                               | p50                                | p90                                |                        | p0                      | p50                          | p90                          |

| tmm           | Caffe2 + CUBLAS<br>ATen + CUBLAS<br>TC (manual)<br>TC (autotuned) | 33<br>35<br>32<br>28         | 35<br>35<br>33<br>29         | 36<br>36<br>35<br>30 | 127<br>120<br>441<br>309   | 134<br>123<br>446<br>313       | 13<br>12<br>46<br>31           | 5 2                            | 3,527<br>3,457<br>4,452<br>4,701 | 3,578<br>3,574<br>24,583<br>14,750 | 3,666<br>3,705<br>24,656<br>14,768 | thmm                   | 340<br>342<br>166<br>96 | 347<br>348<br>170<br>101     | 350<br>353<br>172<br>110     |

| tmm           | Caffe2 + CUBLAS<br>ATen + CUBLAS<br>TC (manual)<br>TC (autotuned) | 29<br>26<br>21<br>24         | 30<br>27<br>22<br>25         | 31<br>27<br>23<br>26 | 107<br>104<br>188<br>107   | 108<br>106<br>194<br>110       | 10<br>10<br>21<br>11           | 0 8                            | 2,404<br>2,395<br>8,378<br>8,130 | 2,431<br>2,409<br>8,402<br>8,177   | 3,068<br>3,043<br>8,411<br>8,251   | thmm                   | 189<br>188<br>91<br>51  | 192<br>190<br>92<br>53       | 197<br>191<br>93<br>54       |

| (N,G,F,C,W,H) |                                                                   | (32, 32, 16, 16, 14, 1       |                              |                      | (32, 32, 32, 32, 7, 7      |                                |                                | 7,7)                           | (32, 32, 4, 4, 56, 56)           |                                    |                                    | (32, 32, 8, 8, 28, 28) |                         |                              |                              |

|               |                                                                   | p0                           | p50                          | p9                   | 0                          | p0                             | p50                            | p90                            | p(                               | p50                                | p90                                |                        | p0                      | p50                          | p90                          |

| gconv         | Caffe2 + CUDNN<br>ATen<br>TC (manual)<br>TC (autotuned)           | 1,672<br>N/A<br>6,690<br>666 | 1,734<br>N/A<br>6,752<br>670 | N/A<br>6,80          | A<br>05 :                  | 1,687<br>N/A<br>3,759<br>1,212 | 1,777<br>N/A<br>3,789<br>1,215 | 1,802<br>N/A<br>3,805<br>1,216 | 4,078<br>N/A<br>2,866<br>1,125   | N/A<br>5 2,930                     | 4,206<br>N/A<br>2,959<br>1,159     | 3,9                    | /A                      | 3,051<br>N/A<br>4,009<br>863 | 3,075<br>N/A<br>4,045<br>870 |

| gconv         | Caffe2 + CUDNN<br>ATen<br>TC (manual)<br>TC (autotuned)           | 1,308<br>N/A<br>3,316<br>319 | 1,343<br>N/A<br>3,339<br>321 | N/A                  | A<br>5 :                   | 1,316<br>N/A<br>2,327<br>691   | 1,338<br>N/A<br>2,348<br>705   | 1,350<br>N/A<br>2,363<br>714   | 4,073<br>N/A<br>1,683<br>464     | N/A<br>3 1,691                     | 4,119<br>N/A<br>1,694<br>504       | 1,8                    | /A                      | 2,021<br>N/A<br>1,870<br>377 | 2,036<br>N/A<br>1,883<br>379 |

Figure 5: Wall-clock execution of kernels (in  $\mu s$ ). Each kernel ran 1000 times. The top half of each table is Tesla M40 (Maxwell) and the bottom half is Tesla P100 (Pascal); N/A indicates the framework lacked an implementation

## **Production Models**

|                 | 1LUT |       |     |     |                 |     | 2LUT            |     |     |  |

|-----------------|------|-------|-----|-----|-----------------|-----|-----------------|-----|-----|--|

|                 | p0   | )     | p50 | p90 | p0              |     | p50             | p90 |     |  |

| Caffe2 + CUBLAS | 78   | 78 80 |     | 82  | 188             |     | 193             | 207 |     |  |

| ATen + CUBLAS   | N/A  |       | N/A | N/A | N/A<br>47<br>47 |     | N/A<br>49<br>49 | N/A |     |  |

| TC (manual)     | 38   | }     | 39  | 40  |                 |     |                 | 52  |     |  |

| TC (autotuned)  | 38   | 3     | 39  | 40  |                 |     |                 | 52  |     |  |

| Caffe2 + CUBLAS | 63   |       | 64  | 66  | 1               | 122 |                 | 128 |     |  |

| ATen + CUBLAS   | N/A  |       | N/A | N/A | N/A             |     | N/A             | N/A |     |  |

| TC (manual)     | 21   |       | 22  | 23  | 30<br>30        |     | 31              | 32  |     |  |

| TC (autotuned)  | 21   |       | 22  | 23  |                 |     | 30              | 31  |     |  |

|                 |      | MLP1  |     |     | С3              |     | MLP3            |     |     |  |

|                 | p0   | p50   | p90 | p0  | p50             | p90 | p0              | p50 | p90 |  |

| Caffe2 + CUBLAS | 123  | 125   | 135 | 146 | 159             | 164 | 124             | 128 | 142 |  |

| ATen + CUBLAS   | 109  | 110   | 112 | 128 | 142             | 148 | 188             | 192 | 213 |  |